發布日期:2022-04-18 點擊率:113

【導讀】目前,嵌入式系統數字化產品成為繼PC機后的信息處理工具。隨著嵌入式技術的發展,圖形處理也從2D圖形向3D圖形轉變。本文采用OpenGL作為系統的圖形API,選取21條基本API命令,定義命令字編碼和渲染列表格式作為IP核的設計規約。

本項目通過在FPGA上用Verilog語言實現3D影像在LCD的成像,具有以下優勢:

1、采用可編程的FPGA進行設計,便于設計的更新與升級,節約成本。

2、緩解CPU在圖形處理方面的負擔。

3、滿足廣大消費者對3D影像的需求

4、LCD體積小、質量輕、功耗低,可以用大規模集成電路直接驅動,可以在明亮環境下顯示,不含射線傷害。

一、實現功能

將IP核劃分為四部分,這里我們分別稱之為FPGA1模塊、FPGA2模塊FPGA3和模塊FPGA4模塊,模擬CPU發送數據的cpu_module需要我們用Verilog HDL設計。Cpu_module和IP核的幾何變換模塊屬于FPGA1模塊,IP核的光照模塊屬于FPGS2模塊,FPGA3模塊則包含了IP核圖形管線的圖元裝配模塊,剔除剪切模塊、背面剔除模塊和投影模塊,IP核圖形管線最后兩個模塊光柵化和片段處理屬于PFGA4模塊。

二、硬件設計

通過上面對整個系統功能要求, 性能要求的分析, 我們可以確定系統的基本硬件結構, 其組成框圖如下所示:

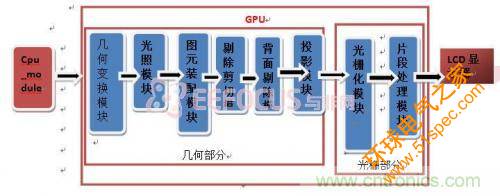

圖1: IP核圖形管線的組成

圖中的cpu module模塊用來模擬圖形應用程序經CPU處理得到渲染列表的過程,它將渲染列表命令以GPU方言的形式送到GPU,并等待圖形管線中8級流水線的處理。整個圖形管線分為兩部分,幾何部分和光柵部分,圖中的前6個模塊幾何變換、光照、圖元裝配、裁剪、背面剔除、投影屬于幾何部分,后2個模塊光柵化和片段處理屬于光柵部分。

三、模塊功能概述

首先是對cpu module送來的數據進行幾何變換,一個三角形圖元由三個頂點構成,每個頂點包含的信息有位置信息、法線信息、顏色信息等。由于三維空間中的物體都是以頂點的形式描述,所以幾何變換模塊主要是對舀Begin和glEnd之間的頂點數據流和相關命令的處理,所做的工作包含對頂點坐標的平移、旋轉、縮放。

然后是對頂點顏色的計算,每個頂點都可以有自己的顏色。影響物體顏色的因素有幾個方面,一是環境光照的影響,二是物體材質本身對光源進行調制,三是光源的位置,因此該級模塊有很多需要根據渲染列表中的命令設置相應的參數,然后按照光照原理和各個模型參數計算出頂點的顏色。頂點的坐標位置和顏色信息有了以后就需要將單獨的頂點數據組裝成一個個圖元,OpenGL支持的圖元有點、線、三角形、折線、線環、三角形帶和三角形扇等。我們的IP核目前只考慮了對三角形圖元的處理,因為三角形是最基本的圖元,其它圖元只要在圖元裝配一級做一些處理就可以轉化為對三角形圖元的處理,點和線段的處理比三角形的處理簡單,只是在光柵化一級稍有不同,而一些復雜圖元則可以分解成三角形圖元來處理。

圖元裝配完成以后就應該對不在視景體內的圖元進行剔除,對部分在視景體內的圖元進行剪切。由于視野的限制,人不可能同時看到所有的物體,舉例來說,你不可能看到自己背后是什么物體,因此在圖形學中用視景體來模擬視野的限制,將一些不顯示的圖元剔除剪切掉,以避免后級不必要的計算,減輕后級的負擔。

背面剔除模塊的工作是判斷圖元的正反面,根據需要顯示我們希望看到的那一面。因為雖然在視景體外面的圖元被剪切掉了,但是并不意味著所有剩下的圖元都會被顯示出來,比如一枚硬幣,當印有人頭的一面對著我們的時候,另一面的字就不能呈現在我們面前,后級的處理也就不需要考慮有字的那一面。

前面五級的處理對象都是三維空間中的頂點數據,但我們的顯示設備只是二維的,這就需要我們將視景體中的三維圖元映射到二維平面上,投影交換模塊的作用就在于此。至此三維圖元就變成了二維的圖元,后面兩級就只需要對二維圖元進行處理。

光柵化一級需要將二維圖元的坐標變換成整數,因為顯示設備的光柵是離散的點陣,該級還需要做的工作是填充圖元的內部,另外圖元邊緣的反走樣也需要在該級完成。經過該級的處理,二元圖元就變成了離散的片元數據,即人們常說的像素數據,每個像素數據都和顯示設備光柵上的某個點一一對應。

最后一級是片段處理,它的工作就是在像素數據送到幀緩沖區之前再對像素數據進行篩選,因為只有符合條件的才會被寫入到幀緩沖區中。比如有一扇門,當門關起來的時候我們就看不見門里的物體,這時只需將描述門的像素數據送到幀緩沖區中,門后面的物體是被門擋住了的,不應該將描述門后物體的像素數據送到幀緩沖區。而當門開著的時候,我們需要將描述門后物體的像素數據送到幀緩沖區中。同時如果需要Alpha混合,則還需要將兩個物體的重疊部分的像素的顏色值做混合處理。

這8個模塊是3D圖形處理器IP核的核心所在,我們的工作就是在課題組已有工作的基礎上,在4塊FPGAJ2用Verilog HDL來設計完善這8個模塊。

四、IP核的驗證平臺

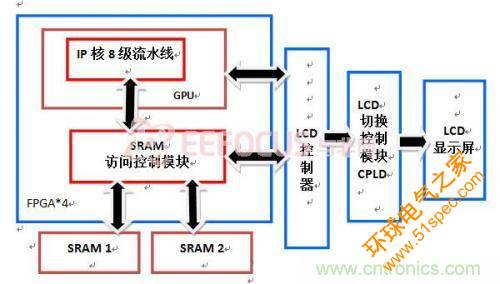

驗證平臺的結構示意圖如圖所示。

圖2:驗證平臺的結構示意圖

驗證平臺所使用的4片FPGA芯片是EP2C20Q240C8,它有18752個邏輯單元和239616BitSMemory,芯片之間采用級聯的形式,按先后順序我們分別用FPGAl、FPGA2、FPGA3、FPGA4來表示。

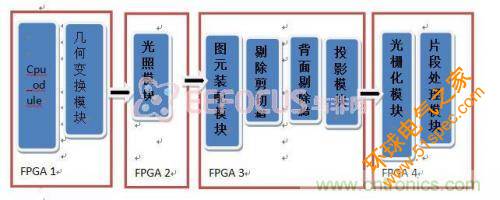

IP核的8個模塊需要按照圖形管線的結構分別映射到4片FPGA中,根據圖形管線各模塊所做的工作,每個模塊在FPGA中的分配如圖3所示。

圖3:IP核各模塊在FPGA中的分配

按照圖中的劃分,我們可以看作是將IP核劃分成了4部分,這里我們分別稱之為FPGAl模塊、FPGA2模塊、FPGA3模塊和FPGA4模塊。由于條件限制,用來模擬CPU發送數據的epu.module也需要我們用Verilog HDL設計,epu 和IP核的幾何變換模塊屬于模塊,口核的光_module FPGAl照模塊屬于FPGA2模塊,FPGA3模塊則包含了IP核圖形管線的圖元裝配模塊、剔除剪切模塊、背面剔除模塊和投影模塊,IP核圖形管線最后兩個模塊光柵化和片段處理屬于FPGA4模塊。

下一篇: PLC、DCS、FCS三大控

上一篇: 一款數控直流穩壓電源