發布日期:2022-04-25 點擊率:48

在設計過程中,元器件設計和PCB布局對電源性能有很大影響。仔細的 PCB 布局對于實現低開關損耗和干凈、穩定的運行至關重要。選擇合適的組件使電源輕松通過 Intel 和 AMD 的規格。本應用筆記將介紹 G-NAVPTM控制拓撲的設計方法,包括導通時間設置、開關頻率設置、負載線設置和 DCR 電流傳感網絡設置。之后,將顯示推薦的 PCB 布局規則,以避免噪聲干擾,使控制器更加穩健。

1.設計方法和元件選擇

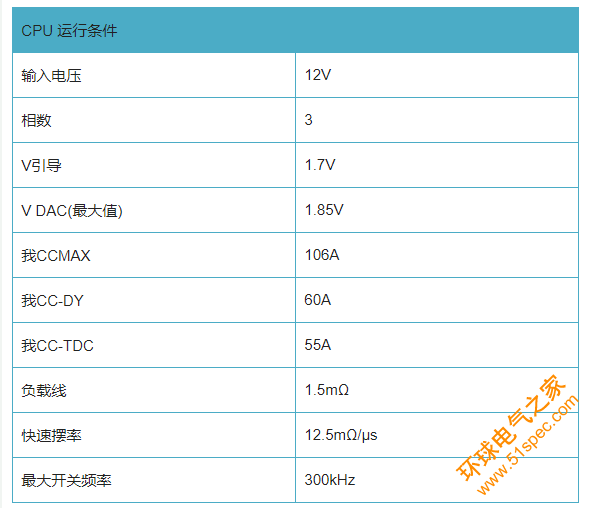

以下設計方法將以 RT8884B 為例,其設計符合 Intel VR12.5 規范。RT8884B 有三個主要的設計程序。第一步是開啟時間和開關頻率的初始設置。第二步是 DCR 電流感應網絡設計。最后,我們要完成負載線設計。

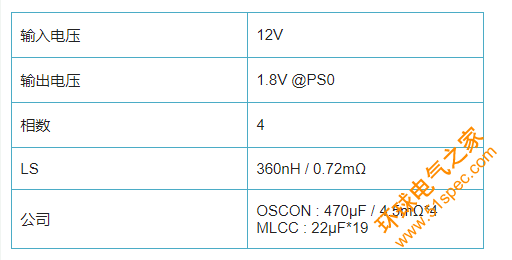

參考 Shark Bay VRTB 供電指南,推薦的輸出濾波器如下:

輸出電感:360nH / 0.72mΩ

輸出大容量電容:560μF / 2.5V / 5mΩ (max) 4 to 5pcs

輸出陶瓷電容:22μF / 0805(頂部最多 18 個站點)

1.1.開啟時間和開關頻率的初始設置

一般來說,更高的開關頻率可以實現更快的瞬態響應,更小的穩態輸出紋波,并減小功率元件的尺寸和PCB空間。然而,較高的開關頻率會導致較低的轉換效率、較差的抗噪性和熱問題。因此,需要將最大開關頻率限制在一個合理的范圍內,以權衡利弊。確定最大開關頻率后,根據占空比與開關頻率的關系,即可得到最大導通時間。

其中VDAC是參考電壓,fsw,max是最大開關,VIN(MAX)是最大輸入電壓。下面是 RT8884B 的設計實例。

由于 RT8884B 是一種恒定導通時間控制,其專利的 CCRCOT(Constant Current Ripple COT)技術可以通過輸入電壓和 VID 代碼生成自適應導通時間,從而獲得恒定電流紋波。從而在不同的輸入和輸出電壓工作范圍內,輸出電壓紋波幾乎可以控制為一個常數。在輸入電壓端和 TonSET 引腳之間連接一個電阻器 RTON以設置導通時間寬度。

其中 C = 18.2pF

其中 VIN是最大輸入電壓,VDAC是參考電壓,ton是導通時間,由上式確定。下面是 RT8884B 的設計實例。

1.2.DCR電流感應網絡設計

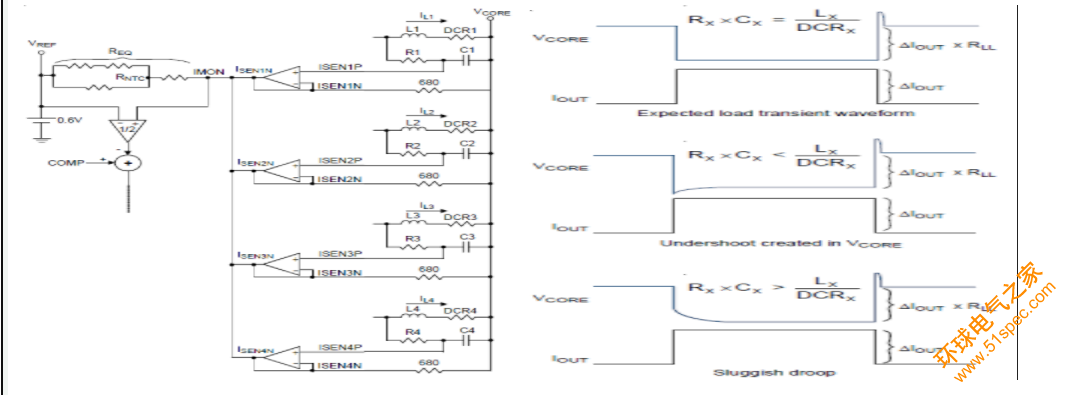

圖 1. RT8884B 的整個電流回路結構。

圖 2. 不同 τCx和 τLx時間常數對應的輸出波形。

圖 1 顯示了 RT8884B 的整個電流回路結構。DCR 電流傳感網絡的設計對 ACLL 性能和 DCLL 精度都起著重要作用。對于不同的時間常數設計,ACLL 行為可以分為以下三個條件。此外,圖 2 顯示了具有不同 τ Cx和 τLx時間常數的相應輸出波形。

? 如果τCx與τLx匹配,則可以設計預期的負載瞬態波形。

? 如果τCx大于τLx,則輸出電壓隨著負載的增加而緩慢下降。

? 如果τCx小于τLx,輸出電壓將下降以減小下沖規范的裕度。

其中 DCRx是電感的等效電阻,Lx是電感的電感量,Rx和 Cx是 DCR 電流檢測網絡參數。

通常,τCx時間常數將被設計為等于或略大于 τLx時間常數,以防止過沖和下沖有更多余量以通過規范。請注意,Cx可能會因偏置電壓、溫度或頻率等因素而衰減。在設計 DCR 電流傳感網絡時,需要考慮對 Cx的衰減影響。

由于電感的銅線具有正溫度系數,DCR值隨著負載電流的增加而線性增加。因此,為了獲得更好的 DCLL 性能,需要一個帶有 NTC 熱敏電阻 (REQ) 的熱補償網絡來補償電感 DCR 的正溫度系數。詳細的熱補償可以參考具體產品的設計工具。

1.3.負載線設計

在 G-NAVPTM拓撲中,負載線設計取決于電流環路增益和電壓環路增益的比率。詳細的負載線方程將顯示在相應的 IC 數據表中。下面以 RT8884B 為例。

其中 DCR (25°C) = 0.72mΩ,RCS= 680Ω是電流感應電阻器,REQ(25°C) 用于熱補償,R2/ R1是補償器 AV增益.通過這個方程,負載線可以簡單地通過調整補償器 AV增益來改變。遵循 Intel VR12.5 規范,需要 1.5 (mW) 負載線;因此,可以確定R2/ R1AV增益。RT8884B 的設計實例如下圖所示。

2.布局考慮

仔細的 PC 板布局對于實現低開關損耗和干凈、穩定的運行至關重要。開關功率級需要特別注意。如果可能,將所有電源組件安裝在電路板的頂部,使其接地端子彼此齊平。請遵循以下指南以獲得最佳 PC 板布局:

2.1. 功率級布局指南

? 保持高電流路徑短,特別是在接地端子處。

? 保持電源走線和負載連接短。這對于高效率至關重要。

? 在電感器的充電路徑和放電路徑之間進行權衡時,最好讓電感器的充電路徑比放電路徑長。

2.2.IC Sensing Pad 和 RGND 布局指南

? 將電流感應元件(CX、RCSX、RX)靠近控制器放置,以避免電流感應信號被噪聲耦合。

圖 3. 電流感應元件的放置。

? 用于電流限制和電壓定位的 ISENxP 和 ISENxN 連接必須使用開爾文檢測連接來保證電流檢測精度。電感器的走線直接從電感器焊盤而不是從電感器的連接平面延伸。

圖 4. 電流感應走線的電感墊。

? 來自電感檢測節點的PCB 走線應并聯回控制器。通常,這些走線位于 PCB 底層的電感器下方。如果這些走線在內層上運行,則電流檢測走線上方必須有一個接地層,作為頂層的屏蔽。

? 將高速開關節點(PWM、UG、LG、相位等)遠離敏感模擬區域(COMP、FB、ISENxP、ISENxN 等)。

? 用戶需要通過低阻抗路徑將裸露焊盤連接到接地層。建議使用至少 5 個過孔連接到 PCB 內部層中的接地層。

三、實驗結果與結論

3.1.實驗結果

圖 5 為 RT8884B EVB 樣例,應用于 VR12.5 應用,支持 4/3/2/1 相位。實測負載線曲線和效率如圖 6 所示。從實測結果來看,G-NAVPTM拓撲可以提供準確的負載線,并且仍然保持較高的效率。圖 7 顯示了一個大階躍和一個小階躍負載瞬態波形,這表明了快速穩定的瞬態性能和適當的 AVP 控制。

圖 5. RT8884B 的 EVB 示例。

表 1. EVB 測試條件

FCI608.png"/>

FCI608.png"/>

圖 6. RT8884B 測得的負載線和效率。

(CH3: 負載電流 (900mv/Div) ; CH4: 輸出電壓 (30mV/Div))

(a) 大步進 (1A-61A) ACLL @300Hz (b) 小步進 (50A-60A) ACLL @300Hz

圖 7. RT8884B 測得的 ACLL 結果

3.2.結論

系統組件的設計通常需要在許多限制之間進行折衷,以在效率和性能上獲得最大收益。此外,特殊的布局技巧用于最大限度地減少寄生元件的影響,避免高速開關噪聲耦合。本應用筆記展示了 G-NAVPTM控制拓撲的一般設計方法和 PCB 布局規則。遵循上述規則,用戶可以毫無不便地使用立锜的控制器IC。

下一篇: PLC、DCS、FCS三大控

上一篇: 海爾抓住顛覆性技術突