發布日期:2022-10-09 點擊率:53

1 引言

DS18B20是DALLAS公司生產的一線式數字溫度傳感器,采用3引腳TO-92型小體積封裝;溫度測量范圍為-55℃~+125℃,可編程為9位~12位A/D轉換精度,測溫分辨率可達0.0625℃,被測溫度用符號擴展的16位數字量方式串行輸出。

一線式(1-WIRE)串行總線是利用1條信號線就可以與總線上若干器件進行通信。具體應用中可以利用微處理器的I/O端口對DS18B20直接進行通信,也可以通過現場可編程門陣列(FPGA)等可編程邏輯器件(PLD)實現對1-WIRE器件的通信。

本文介紹利用ACTEL公司的ProASICplus系列FPGA實現與DS18B20的通信功能。FPGA可以將讀出DS18B20的48位ID號和12位溫度測量結果保存在內部寄存器中,微處理器可以隨時快速地從FPGA寄存器中讀取這些信息。

一般在使用DS18B20時往往采用微處理器的I/O端口實現與該器件的通信,這種方法雖然比較容易和方便,但是,因為DS18B20的一線式串行總線對時序要求比較嚴格,因此,為了保證與DS18B20的通信可靠性,微處理器與DS18B20通信時需要采用關閉中斷的辦法,以防止操作時序被中斷服務破壞。

利用FPGA實現與DS18B20通信不存在被迫關閉中斷的情況,可以滿足對實時性要求嚴格的應用要求。

2 ProASICplus系列FPGA簡介

ProASICplus系列FPGA是ACTEL公司推出的基于Flash開關編程技術的現場可編程門陣列,包括從7.5萬門的APA075型到100萬門的APAl000型,具有高密度、低功耗、非易失、含有嵌入式RAM及可重復編程等特點。

因為ProASICplus系列FPGA基于Flash技術,利用Flash開關保存內部邏輯,因此不需要另外的器件。由于不需要上電配置過程,因此具備上電就立即工作的特點。不用配置器件,系統的保密性提高。

筆者在電力監控的產品中利用APA150型FPGA實現了邏輯控制、A/D采樣控制和FIFO存儲等功能,并利用剩余的資源實現了DS18B20的通信功能。APA150在整個系統中充當協處理器,使主CPU從繁重的實時處理中解脫出來。

3 DS18B20簡介

3.1內部結構

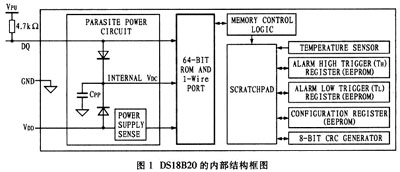

DS18B20的內部結構如圖1所示,主要由以下幾部分組成:64位ROM、溫度傳感器、非揮發的溫度報警觸發器TH(溫度高)和TL(溫度低)、配置寄存器、暫存寄存器(SCRATCHPAD)、存儲器控制邏輯。DQ為數字信號輸入/輸出端。

ROM中的64(8位產品家族編號、48位ID號、8位CRC)位序列號是出廠前刻好的,這64位序列號具有惟一性,每個DS18B20的64位序列號均不相同。

8位CRC生成器可以完成通信時的校驗。

暫存寄存器有9個字節,包含溫度測量結果、溫度報警寄存器、CRC校驗碼等內容。

3.2操作步驟

對DS18B20的操作分為3個步驟:初始化、ROM命令和DS18B20功能命令。

3.2.1初始化

FPGA要與DS18B20通信,首先必須完成初始化。FPGA產生復位信號,DS18B20返回響應脈沖。

3.2.2ROM命令

該步驟完成FPGA與總線上的某一具體DS18B20建立聯系。ROM命令有搜尋ROM(SEARCH ROM)、讀ROM(READ ROM)、匹配ROM(MATCH ROM)、忽略ROM(SKIP ROM)、報警查找等命令(ALARM SEARCH)。

這里,FPGA只連接1個DS18B20,因此只使用讀ROM命令,來讀取DS18B20的48位ID號。

3.2.3 DS18B20功能命令

FPGA在該步驟中完成溫度轉換(CONVERTT)、寫暫存寄存器(WRITE SCRATCHPAD)、讀暫存寄存器(READ SCRATCHPAD)、拷貝暫存寄存器(COPYSCRATCHPAD)、裝載暫存器寄存器(RECALL E2)、讀供電模式命令(READ POWER SUPPLY)。

文中不用溫度報警功能,因此在本步驟中只需完成溫度轉換,然后通過讀暫存寄存器命令完成溫度轉化的結果。

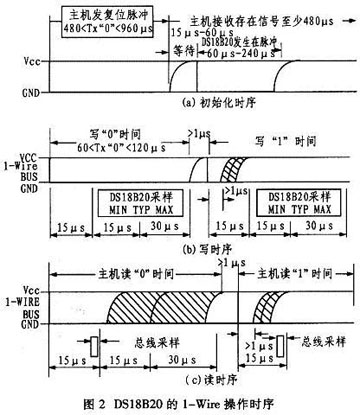

3.3操作時序

2所示。從時序圖中可以看出,對DS18B20的操作時序要求比較嚴格。利用FPGA可以實現這些操作時序。

4 FPGA與DS18B20的通信

4.1 DS18B20的操作模塊

FPGA需要完成DS18B20的初始化、讀取DS18B20的48位ID號、啟動DS18B20溫度轉換、讀取溫度轉化結果。讀取48位ID號和讀取溫度轉換結果過程中,FPGA還要實現CRC校驗碼的計算,保證通信數據的可靠性。

以上操作反復進行,可以用狀態機來實現。狀態機的各種狀態如下:

RESET1:對DS18B20進行第一次復位,然后進入DELAY狀態,等待800μs后,進入CMD33狀態。

CMD33:對DS18B20發出0×33命令,讀取48位ID值。

GET_ID:從DS18B20中讀取48位ID值。

RESET2:對DS18B20進行第二次復位,然后進入DELAY狀態等待800μs后,進入CMDCC狀態。

CMDCC:向DS18B20發出忽略ROM命令,為進入下一狀態作準備。

CMD44:向DS18B20發出啟動溫度轉換命令,然后進入DELAY狀態等待900ms后進入下一狀態。

RESET3:對DS18B20進行第三次復位。

CMDCC2:

向DS18B20發出忽略ROM命令,為了進入下一狀態作準備。

GET_TEMP:從DS18B20中讀取溫度測量數值。

DELAY:等待狀態。

WRITE_BIT:向DS18B20中寫入數據位狀態。

READ_BIT:從DS18B20中讀取數據位狀態。在該狀態中每讀取1位數據,同時完成該數據位的CRC校驗計算。所有數據都讀取后,還要讀取8位CRC校驗位。這8位校驗位也經過CRC校驗計算,如果通信沒有錯誤,總的CRC校驗結果應該是0。這時可將通信正確的數據保存到id和temp_data寄存器中。

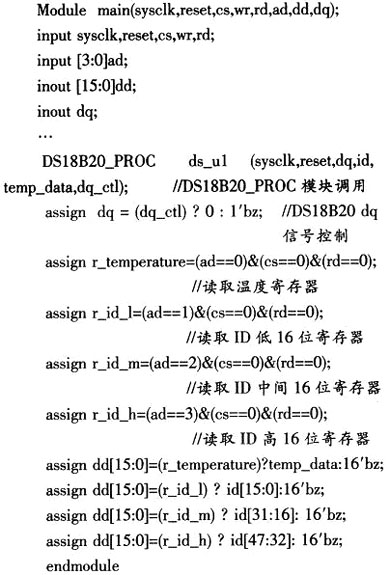

設計中采用Verilog語言建立DS18B20操作模塊”DS18B20_PROC”。在該模塊中實現以上的狀態機功能。該模塊的定義為module DS18B20 PROC(sysclk,reset,dq_pim,id,temp_data,dq_ctl)。

從仿真波形可以看出,系統上電后的10ms左右,FPGA可以讀出DS18B20的48位ID值,這樣,主CPU在系統復位后很短的時間內就可以讀取ID值,進行相應的處理。

4.2 FPGA與CPU的接口

在FPGA中,要實現對DS18B20的通信處理,主模塊要實現對DS18B20_PROC模塊的調用及建立與CPU之間的接口。

與CPU之間的接口通過建立若干寄存器實現。溫度測量值和48位ID可以用4個16位寄存器保存。CPU通過讀取這些寄存器可以獲得溫度測量數值和48位ID值。

CPU、FPGA及DS18B20的連接原理如圖4所示。

5 結束語

在系統中,FPGA可以分擔許多主處理器的工作,提高整體實時性,降低CPU處理的嚴格實時約束,從而降低CPU軟件處理的難度。同時,由于ACTEL公司的ProASICplus系列FPGA的保密特性,可以增強產品知識產權的保護。

本設計應用在電力監控產品中。測量出的裝置內部溫度用于電量測量精度補償和報警,對保證產品測量精度和可靠運行具有重要意義。48位ID值用于產品的惟一編碼標識和以太網MAC地址,便于產品生產、維護和管理。

下一篇: PLC、DCS、FCS三大控

上一篇: 橡膠拉力試驗機如何選