發布日期:2022-10-18 點擊率:55

有限脈沖響應(FIR)和無限脈沖響應(IIR)濾波器都是常用的數字信號處理算法 --- 尤其適用于音頻處理應用。因此,在典型的音頻系統中,處理器內核的很大一部分時間用于 FIR 和 IIR 濾波。數字信號處理器上的片內 FIR 和 IIR 硬件加速器也分別稱為 FIRA 和 IIRA,我們可以利用這些硬件加速器來分擔 FIR 和 IIR 處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。

簡介

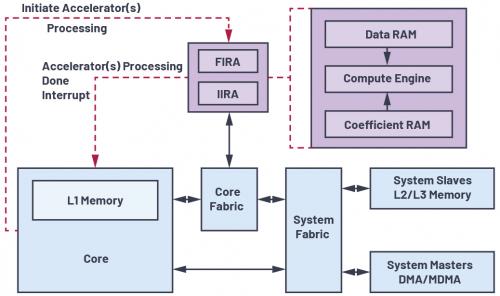

圖 1.FIRA 和 IIRA 系統方框圖

圖 1 顯示了 FIRA 和 IIRA 的簡化方框圖,以及它們與其余處理器系統和資源的交互方式。

在本文中,我們將討論針對不同應用場景充分利用這些加速器的各種模型。

實時使用 FIRA 和 IIRA

圖 2. 典型實時音頻數據流

圖 2 顯示了典型實時 PCM 音頻數據流圖。一幀數字化 PCM 音頻數據通過同步串行端口(SPORT)接收,并通過直接存儲器訪問(DMA)發送至存儲器。在繼續接收幀 N+1 時,幀 N 由內核和 / 或加速器處理,之前處理的幀(N-1)的輸出通過 SPORT 發送至 DAC 進行數模轉換。

加速器使用模型

如前所述,根據應用的不同,可能需要以不同的方式使用加速器,以最大限度分擔 FIR 和 / 或 IIR 處理任務,并盡可能節省內核周期以用于其他操作。從高層次角度來看,加速器使用模型可分為三類:直接替代、拆分任務和數據流水線。

直接替代

拆分任務

如圖 3 所示,與直接替代模型相比,此使用模型可節省更多的內核周期。

數據流水線

圖 3 說明了音頻數據幀如何在不同加速器使用模型的三個階段之間傳輸 ---DMA IN、內核 / 加速器處理和 DMA OUT。它還顯示了通過采用不同的加速器使用模型將 FIR/IIR 全部或部分處理轉移到加速器上,與僅使用內核模型相比,內核空閑周期如何增加。

圖 3. 加速器使用模型比較

SHARC 處理器上的 FIRA 和 IIRA

以下 ADI SHARC?處理器系列支持片內 FIRA 和 IIRA(從舊到新)。

https://www.analog.com/en/search.html?q=ADSP-214xxADSP-214xx? (例如, https://www.analog.com/cn/products/adsp-21489.htmlADSP-21489)

https://www.analog.com/cn/products/landing-pages/001/adsp-sc58x-adsp-2158x-series.htmlADSP-SC58x

https://www.analog.com/cn/products/landing-pages/001/adsp-sc57x-2157x-family.htmlADSP-SC57x? /https://www.analog.com/cn/products/landing-pages/001/adsp-sc57x-2157x-family.htmlADSP-2157x

https://www.analog.com/cn/products/landing-pages/001/adsp-2156x-family.htmlADSP-2156x

這些處理器系列:

ADSP-2156x 處理器上的 FIRA/IIRA 改進

ADSP-2156x 是 SHARC 處理器系列中的最新的產品。它是第一款單核 1 GHz SHARC 處理器,其 FIRA 和 IIRA 也可在 1 GHz 下運行。ADSP-2156x 處理器上的 FIRA 和 IIRA 與其前代 ADSP-SC58x/ADSP-SC57x 處理器相比,具有多項改進。

功能改進

添加了 ACM 支持,以盡量減少進行加速器處理所需的內核干預。此模式主要具有以下新特性:

實驗結果

在本節中,我們將討論在 ADSP-2156x 評估板上,借助不同的加速器使用模型實施兩個實時多通道 FIR/IIR 用例的結果

用例 1

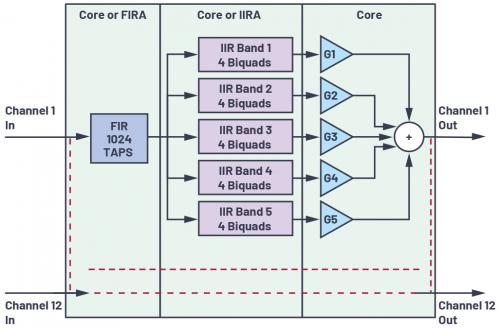

圖 4 顯示用例 1 的方框圖。采樣率為 48 kHz,模塊大小為 256 個采樣點,拆分任務模型中使用的內核與加速器通道比為 5:7。

表 1 顯示測得的內核和 FIRA MIPS 數量,以及與僅使用內核模型相比獲得的節約內核 MIPS 結果。表中還顯示了相應使用模型增加的額外輸出延遲。正如我們所看到的,使用加速器配合數據流水線使用模型,可節約高達 335 內核 MIPS,但導致 1 塊(5.33 ms)的輸出延遲。直接替代和拆分任務使用模型也分別可節約 98 MIPS 和 189 MIPS,而且未導致任何額外的輸出延遲。

圖 4. 用例 1 方框圖

表 1. 用例 1 的內核和 FIR/IIRA MIPS 總結

用例 2

圖 5 顯示用例 2 的方框圖。采樣率為 48 kHz,模塊大小為 128 個采樣點,拆分任務模型中使用的內核與加速器通道比為 1:1。

與表 1 一樣,表 2 也顯示了此用例的結果。正如我們所看到的,使用加速器配合數據流水線使用模型,可節約高達 490 內核 MIPS,但導致 1 模塊(2.67 ms)的輸出延遲。拆分任務使用模型可節約 234 內核 MIPS,而沒有導致任何額外輸出延遲。請注意,與用例 1 中不同,在用例 2 中內核使用頻域(快速卷積)處理,而非時域處理。這就是為何處理一個通道所需的內核 MIPS 比 FIRA MIPS 少的原因,這可導致直接替代使用模型實現負的內核 MIPS 節約。

圖 5. 用例 2 方框圖

表 2. 用例 2 的內核和 FIR/IIRA MIPS 總結

結論

在本文中,我們看到如何利用不同的加速器使用模型實現所需的 MIPS 和處理目標,從而將大量內核 MIPS 轉移到 ADSP-2156x 處理器上的 FIRA 和 IIRA 加速器。

下一篇: PLC、DCS、FCS三大控

上一篇: 5G的NSA和SA,到底啥